Исследования в области архитектуры модульных асинхронных развиваемых систем вступили в новую фазу - активного макетирования и создания экспериментальных и прототипных образцов. Эта фаза должна закончиться проверкой основных системных и технических решений на макете системы, в архитектуре которой будут присутствовать все основные элементы концепции [I].

Разрабатываемый в рамках ВНТК СТАРТ комплекс технических средств модульной асинхронной развиваемой архитектуры (МАРС) ориентирован на создание параллельных ЭВМ класса супермини и высокопроизводительных рабочих станций. На базе этих средств создается несколько макетных конфигураций, представляющих вычислительные системы с архитектурой МАРС, снабженные необходимым составом периферийного оборудования и средств связи.

Разрабатываются две основные конфигурации технических средств с последующим их тиражированием для внутренних и внешних целей:

- базовая, которая в дальнейшем будет называться макетом МАРС;

- инструментальная на основе 32-разрядной микроЭВМ с шиной Multibus.

Конфигурации должны быть совместимы по системе команд, и на них должна ставиться операционная система ОС МАРС. Базовая конфигурация (макет МАРС) является параллельной многофункциональной ЭВМ высокой производительности с параллельной транспьютерной организацией, большим объемом памяти, со средствами связи и с включенными в конфигурацию мини-, микроэвм и спецпроцессорами, выполняющими специфические системные функции (диагностику, пульт, управление внешней памятью и вводом/выводом). Инструментальная конфигурация ориентирована на разработку программного обеспечения и использование в качестве специализированных рабочих станций в прикладных разработках (САПР СБИС, экспертные системы и др.).

1. Технические средства макета МАРС

В состав макета МАРС входят следующие основные компоненты:

- мультипроцессорное ядро, построенное на базе процессоров Кронос с использованием транспьютерной организации;

- модуль общей памяти;

- мини-ЭВМ, выполняющая функции архивной подсистемы;

- диагностическая ЭВМ, пульт системы;

- специализированные средства.

Основа системы - мультипроцессорное ядро - структурно реализуется как совокупность так называемых транспьютерных узлов, связанных между собой сетью асинхронных каналов, позволяющих осуществлять прямые межпроцессорные передачи данных. В свою очередь, транспьютерные узлы объединяют с помощью системной шины ряд транспьютерных модулей, в частности, процессоров. Такая иерархия позволяет балансировать соотношения объемов вычислений и объемов передаваемых данных путем увеличения или уменьшения числа процессоров в транспьютерных узлах и изменения сети асинхронных каналов.

Процессорный модуль Кронос-2.5 [2] имеет систему команд, ориентированную на реализацию языков высокого уровня (Мо-дуль-2, С, Паскаль, Ада и др.). Модуль имеет 32-разрядную архитектуру, содержит относительно большую локальную оперативную память объемом 0,5 Мбайт, имеет необходимые средства для взаимодействия с другими модулями. Эта система команд в ее 16-разрядном варианте была предложена Н.Виртом [3] для персональной микроЭВМ Lilith. При адаптации системы команд к 32-разрядной архитектуре и макету МАРС была несколько изменена модель памяти в сторону увеличения степени перемещаемости кода и данных, добавлен ряд полезных команд и механизмы транспьютерной организации. Аппаратные средства процессора включают также диспетчер памяти и интерфейс с внутренней шиной.

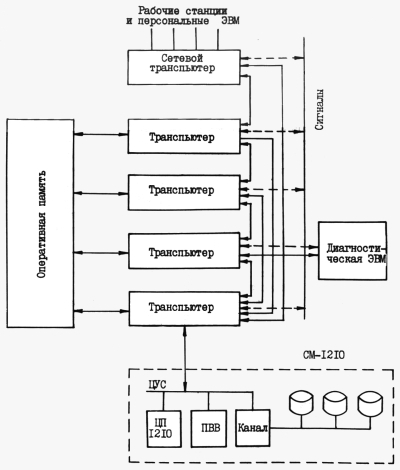

Общая структурная схема макета МАРС приведена на рисунке. В качестве модуля общей памяти предполагается использовать МГП (модуль главной памяти) ЭВМ ПС-3000. Он имеет объем четыре порта в потоковом режиме, что весьма важно для данной архитектуры.

Архивные функции будут возложены на ЭВМ CM-I2I0, оснащенную 29-Мбайтными дисками и магнитофонами. Связь между ядром системы и CM-I2I0 осуществляется через интерфейс между системной шиной транспьютерного узла и шиной ИУС. Машина имеет большую оперативную память и неплохое быстродействие, что дает возможность использовать ее также для выполнения ряда других общесистемных функций и обслуживания пользовательских терминалов.

Распределенная асинхронная архитектура нуждается в хороших средствах диагностики и управления оборудованием. Эти функции возлагаются на специальную диагностическую микроЭВМ. Она непосредственно подключается к диагностическим шинам транспьютерных узлов, через которые ведет анализ ситуации, обработку событий, управление сбросом, инициацией, осуществляет приостановку отдельных модулей и всей системы. Диагностическая ЭВМ также должна иметь штатный вход в систему через асинхронные каналы для взаимодействия с операционной системой комплекса.

Подключение внешних ЭВМ и рабочих станций осуществляется через сетевые средства. Для обеспечения комплекса средствами связи разрабатывается специальный сетевой процессор, построенный по тем же архитектурным принципам, что и остальные части системы и оформленный как транспьютерный узел. В функции этого процессора входит поддержка аппаратурой и программным обеспечением сетевых протоколов нижних уровней, и таким образом ОС МАРС будет обеспечена нужным спектром сетевых примитивов. Существенным требованием к сетевому программному обеспечению является требование возможности создания распределенных программных систем.

Макет системы МАРС

Важная роль в макете МАРС отводится поддержке высокопроизводительных вычислений над числами с плавающей точкой и векторно-матричных вычислений. Для этого, с одной стороны, разрабатывается 64-разрядный арифметический расширитель для базового процессора Кронос, а с другой стороны, предполагается подключение к системе параллельного процессора МАРС-М. Наличие быстродействующего арифметического расширения на ряде процессоров комплекса даст возможность распараллеливать программы пользователей и получать за счет этого выигрыш во времени решения задач. В этом смысле более традиционным путем может оказаться включение векторного процессора типа ЕС-2706 (или ряда процессоров) в конфигурацию. Программы при этом распадаются на векторные процедуры, исполняемые на спецпроцессоре, и основные скалярные вычисления, снабженные вызовами векторных процедур. Наличие обширных библиотек для таких процессоров существенно облегчит их адаптацию к системе.

Схема включения специализированных процессоров достаточно проста и естественна - осуществляются аппаратные и программные доработки для оформления устройства или процессора в виде транспьютерного узла и подключение его к ядру системы через совокупность асинхронных каналов.

Та же задача поддержки высокопроизводительных научно-технических расчетов, но на качественно ином уровне, решается в высокопроизводительном процессоре для научных расчетов МАРС-М [4] . Это большая машина, приближающаяся к классу суперкомпьютеров, способная решать с весьма высокой производительностью векторные и скалярные задачи обработки чисел с плавающей точкой и смеси таких задач. Тесное включение этого процессора в конфигурацию системы МАРС позволит эффективно осуществлять основные системные функции, включая трансляцию, на приспособленных для этой цели процессорах ядра, а собственно счет таких задач вести на МАРС-М. Основной проблемой такого объединения, которую предстоит решить, является обеспечение большой пропускной способности прямой передачи данных через асинхронные каналы.

2. Транспьютерная организация

Ядро системы разрабатывается в виде модулей, объединяемых с помощью единого интерфейса. Модули группируются в транспьютерные узлы и подсистемы с использованием специализированных и универсальных шин. Межшинные интерфейсы позволяют организовать единую работу транспьютерных узлов и подсистем в рамках различных конфигураций. Основным интерфейсным средством между транспьютерными узлами служит асинхронный канал.

Отличие транспьютерных модулей от традиционных процессоров и транспьютерных узлов от существующих шинных структур заключается в существенно большей ориентации на аппаратную поддержку распределенных потоковых вычислений и мультипроцессирование. Это выражается в появлении специальных средств прямой межмодульной передачи данных - асинхронных каналов и аппаратно-микропрограммных средств быстрого переключения процессов.

Транспьютерные узлы и подсистемы могут иметь локальную память и доступ к общей оперативной памяти через специальные средства. Большие параллельные конфигурации оснащаются специализированными средствами диагностики и первичного управления, локализованными в диагностической ЭВМ.

Со стороны пользователя система выглядит как набор модулей, взаимодействующих между собой через сеть связи высокой пропускной способности. Каждый модуль имеет некоторую внутреннюю структуру, выход на сеть связи и может иметь выход на общую оперативную память. Выход на сеть связи осуществляется через входные и выходные очереди. Работа модуля в рамках системы заключается в обработке данных общей оперативной памяти и входных потоков информации, получаемых из входных очередей с выработкой выходных потоков, помещаемых в выходные очереди. Система связи обеспечивает статическое, изменяемое только в периоды перегенерации системы соответствие: выходная очередь одного модуля - входная очередь другого (как случай того же модуля). Это соответствие будем называть связью.

Связи являются буферизованными в том смысле, что данное попадает в порт-приемник не мгновенно, а после прохождения через сеть. Кроме того, одновременно по связи может продвигаться не одно данное, а конечное их число. Глубина буферизации не фиксируется на логическом уровне и определяется реализацией. Естественным требованием является ненарушение порядка: первый вошел в связь - первый вышел. Из-за конечности буфера в связи могут возникать тупиковые ситуации. Это нужно учитывать при программировании и в операционной системе.

Среди модулей выделяются процессорные, интерфейсные и специальные. Процессорные модули представляют собой процессор Кронос-2.5, оснащенный локальной памятью, необходимыми средствами выхода на сеть связи и доступа к общей оперативной памяти; интерфейсные служат для согласования различных шин и являются элементами сети связи; специальные выполняют некоторые функции в системе с использованием специального оборудования (спецпроцессоры, сетевые процессоры, контроллеры и т.д.).

3. Операционная система

В соответствии с общими принципами архитектуры модульных развиваемых систем, операционная система должна обеспечивать:

- эффективное функционирование тесно связанного комплекса разнородных по функциям процессоров без снижения интегральной производительности за счет потерь на организацию межпроцессорных взаимодействий;

- легкое подключение новых модулей и простоту изменения конструкции;

- возможность порождения активно взаимодействующих параллельных процессов, исполняемых на динамически меняющемся числе процессоров.

Операционная система должна быть высоко надежной, модифицируемой и позволять легко адаптировать существующее программное обеспечение.

Для достижения этих целей нужно изменить традиционно сложившуюся структуру ОС как единого замкнутого комплекса программ. В ОС МАРС выделяется ядро - минимальная система модулей, предоставляющая системам программирования набор высокоуровневых операций, связывающих системы программирования с оборудованием. Ядро ОС является открытым и развиваемым.

На основе ядра ОС функционируют базовые системы программирования, являющиеся, по существу, виртуальными машинами, предоставляющими программисту возможность создания требуемой программной обстановки. Для макета системы МАРС реализуются две базовые системы программирования:

- обеспечивающая совместимость с ОС UNIX,

- оригинальная базовая, создающая программную обстановку с основным языком Модула-2.

В рамках базовых систем создаются проблемно- или языково-ориентированные системы программирования, а уже на их основе - прикладные пользовательские системы. Такая иерархическая модульная структура системного программного обеспечения решает ряд проблем программирования, возникающих при переходе к ЭВМ новой архитектуры, особенно многопроцессорной и с включением в систему специализированных процессоров.

Литература

- Марчук Г.И., Котов В.Е. Модульная асинхронная развиваемая система (МАРС): Препринт № 86, 87. - Новосибирск, 1978. - 48 с., 51 с. - В надзаг.: ВЦ СО АН СССР.

- Кузнецов Д.Н. и др. Процессор Кронос в мультипроцессорной системе. - Наст. сб., с. 13-19.

- Wirth N. The personal computer Lilith. Report 40. Zurich: Swiss Federal Institute of Technology, 1981.

- Вишневский Ю.Л. Архитектурные особенности процессора Мини-МАРС. - В кн.: Высокопроизводительные системы обработки больших массивов данных. Новосибирск, 1982, с.5-33.